3D‑staplade chip och dess integration som nästa arkitekturrevolution

Framtidens chipdesign ritar om gränserna för prestanda och energieffektivitet. Istället för att sprida komponenter över stora ytor på ett planat kretskort, bygger 3D-staplade chip flera lager av transistorer och funktioner ovanpå varandra. Denna arkitekturrevolution gör det möjligt att minska avståndet mellan komponenter, snabba upp signaler och packa mer kraft på mindre yta. Samtidigt öppnar den för nya möjligheter inom AI, datacenter och avancerad konsumentelektronik. Men den nya dimensionen innebär också utmaningar kring värmehantering, tillverkningskomplexitet och skalbarhet. Att förstå 3D-integration är därför avgörande för att hänga med i nästa generations hårdvaruevolution.

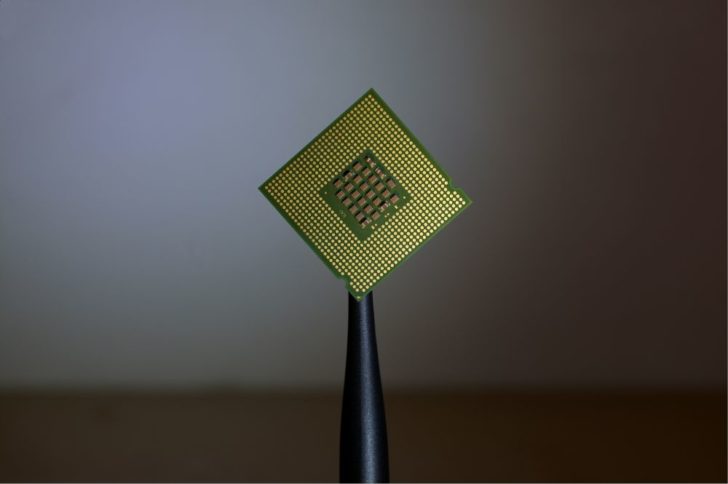

Vad är 3D-staplade chip och hur fungerar de?

3D-staplade chip representerar ett av de mest spännande framstegen inom modern halvledarteknik. Till skillnad från traditionella kretsar byggs flera lager av transistorer och funktioner ovanpå varandra, vilket skapar en vertikal struktur. Detta innebär att komponenter som tidigare låg på samma plan kan kommunicera snabbare, använda mindre energi och ta upp mindre utrymme på kretskortet. Tekniken öppnar dörren för mer komplexa system, från avancerad AIbearbetning till högpresterande datacenter. Förståelsen av hur dessa lager samverkar är grundläggande för att kunna dra nytta av de möjligheter som 3Dintegration erbjuder.

Principer bakom vertikal integration

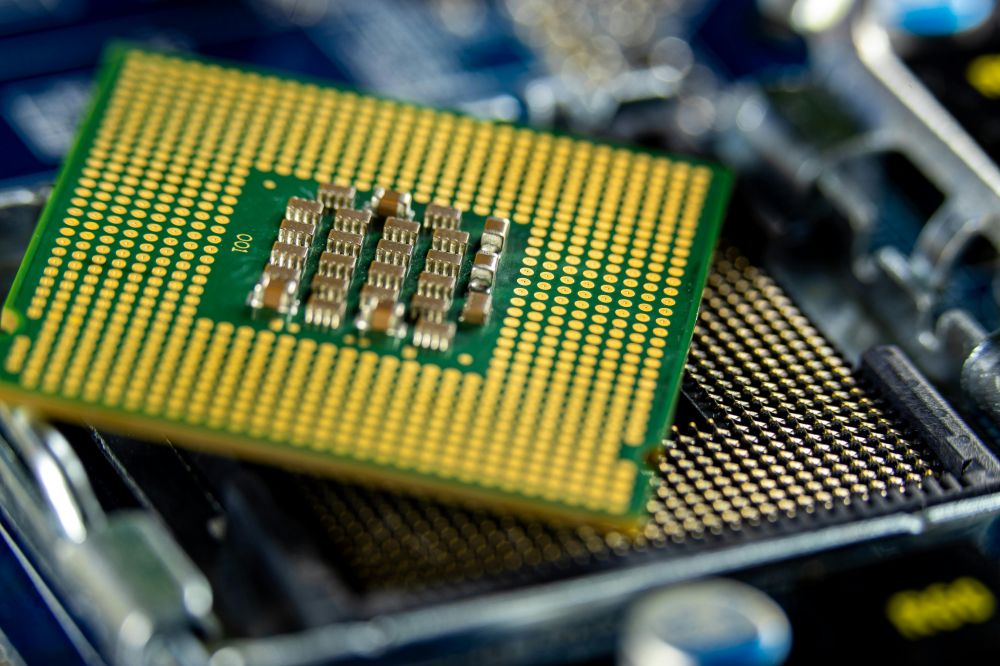

I ett 3D-staplat chip kopplas flera lager samman med hjälp av vertikala ledningar, ofta kallade throughsilicon vias (TSV). Dessa leder elektriska signaler direkt mellan lager, vilket drastiskt minskar fördröjningen jämfört med traditionella horisontella kopplingar. Genom att korta avståndet mellan transistorer kan signaler färdas snabbare och med mindre energiförlust.

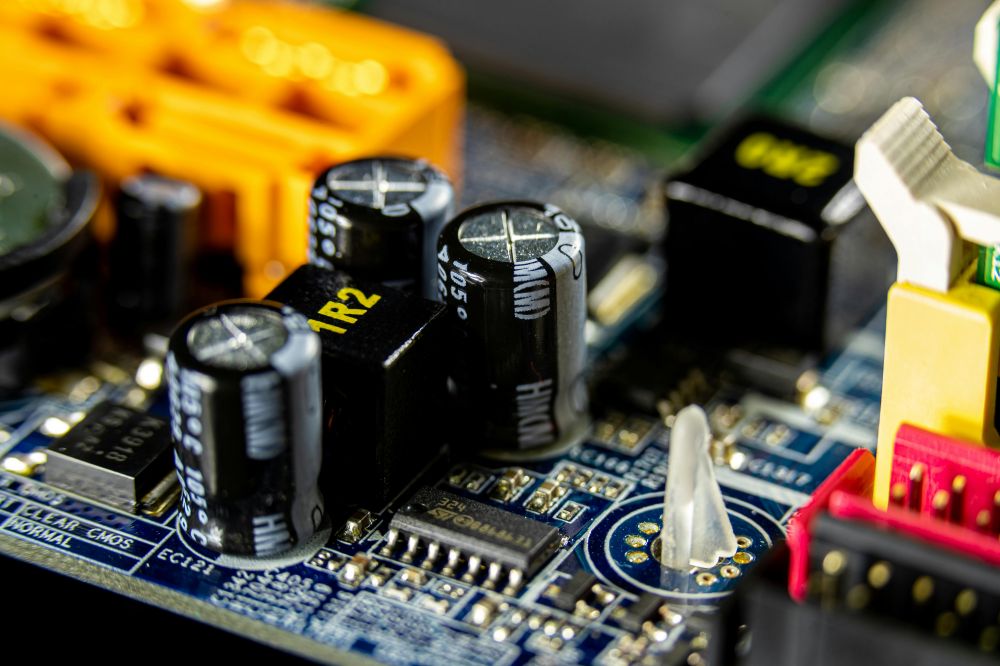

Varje lager kan ha specialiserade funktioner: ett lager kan hantera minne, ett annat beräkningar och ett tredje kommunikation. Denna separation av funktioner möjliggör optimering av varje lager efter dess uppgift. Samtidigt kräver det noggrann design för att säkerställa att värme och elektriska störningar hanteras korrekt.

Material och tillverkning

Tillverkningen av 3D-chip är mer komplex än traditionella planarchip. Den kräver avancerade tekniker för att stapla tunna kiselplattor och skapa pålitliga elektriska förbindelser mellan dem. Materialval är avgörande för både prestanda och hållbarhet, och varje lager måste tåla värme och mekanisk stress under både tillverkning och användning.

-

Genomlysning av lager för precision krävs under produktion.

-

Användning av isolerande material mellan lager förhindrar kortslutning.

-

Metalledningar som TSV skapar vertikal signalöverföring.

-

Termiska sprickor måste undvikas med noggrann design.

-

Testning av varje lager säkerställer funktion innan slutlig integration.

Fördelar med vertikal integration i modern chiparkitektur

3D-staplade chip erbjuder flera konkreta fördelar som gör dem attraktiva för avancerad hårdvara. Den mest uppenbara är densitet: fler transistorer kan packas på samma yta, vilket ger högre prestanda utan att öka fysisk storlek. Detta är särskilt viktigt i bärbara enheter och datacenter där utrymme är en begränsande faktor. Dessutom minskar avstånden mellan komponenter energiförlusten och ökar hastigheten på databehandling, vilket är kritiskt för AI och realtidsapplikationer.

Effektivitet och prestanda

Kortare signalvägar innebär snabbare beräkningar och mindre energiförbrukning. Vertikal integration möjliggör också specialisering av lager, vilket gör att varje funktion kan optimeras utan kompromiss med andra delar. Detta ger en flexibilitet som planarchip inte kan matcha.

Högre densitet ger också möjlighet att integrera minne närmare processorkärnorna, vilket minskar latens och förbättrar systemprestanda. Denna närhet är avgörande för AIalgoritmer som kräver snabb tillgång till stora datamängder.

-

Mer funktion på samma kretsyta sparar utrymme.

-

Snabbare signaler minskar energiförlust och latens.

-

Specialiserade lager ger optimerad prestanda per funktion.

-

Integrerat minne nära processorer förbättrar hastighet.

-

Möjliggör mer komplexa system utan större fysisk storlek.

Kompatibilitet med framtida teknik

3D-staplade chip är också bättre rustade för framtida teknologier, som kvantdatorer och avancerad AI. Den vertikala designen gör det lättare att lägga till nya lager eller komponenter utan att omarbeta hela chipet. Detta skapar en flexibilitet som kan förlänga livslängden och relevansen för tekniken i flera generationer.

Utmaningar och framtida möjligheter för 3D-chipteknik

Trots de många fördelarna med 3D-chip finns betydande utmaningar kvar innan tekniken kan bli standard i alla typer av hårdvara. Tillverkning är dyrare och mer komplex än traditionella chip, och vertikal integration medför problem med värmehantering. När flera lager ligger tätt sammanpressade genereras mer värme per volymenhet, vilket kräver avancerade kylmetoder för att undvika överhettning och försämrad livslängd.

Skalbarhet och produktion

Att skala upp produktionen av 3D-chip är en annan utmaning. Varje lager måste tillverkas med extrem precision, och fel i ett lager kan leda till att hela chipet blir oanvändbart. Testning och kvalitetskontroll blir därför mer kritisk och resurskrävande än för planarchip.

Hantering av variationer i material och limning mellan lager påverkar också skalbarhet. Tillverkare investerar i nya metoder för att säkerställa repeterbarhet och hög yield, vilket är avgörande för kommersiell framgång.

-

Värmehantering kräver innovativa kylsystem.

-

Produktion med hög precision ökar kostnader.

-

Testning av fler lager är mer komplex och tidskrävande.

-

Materialvariationer måste kontrolleras noggrant.

-

Skalbarhet kräver automatiserade och pålitliga processer.

Framtida möjligheter

När tekniska hinder övervinns kan 3D-staplade chip möjliggöra helt nya typer av enheter med extremt hög prestanda i kompakt format. AI, datacenter, bärbar elektronik och avancerade sensornätverk kommer alla att dra nytta av vertikal integration. Genom att kombinera hög densitet, snabb signalöverföring och energieffektivitet kan 3D-chip bli hjärtat i nästa generation av hårdvaruinnovationer.

FAQ

Vad är ett 3D‑staplat chip?

Vilka fördelar ger 3D‑chip jämfört med planarchip?

Vilka utmaningar finns med 3D‑chipteknik?

Fler nyheter

Journalsystem veterinär nyckeln till en tryggare och smidigare djurvård

Framtidens chipdesign ritar om gränserna för prestanda och energieffektivitet. Istället för att sprida komponenter över stora ytor på ett planat kretskort, bygger 3D-staplade chip flera lager av transistorer och funktio...

04 mars 2026

Videoproduktion som skapar upplevelser från idé till färdig sändning

Framtidens chipdesign ritar om gränserna för prestanda och energieffektivitet. Istället för att sprida komponenter över stora ytor på ett planat kretskort, bygger 3D-staplade chip flera lager av transistorer och funktio...

02 mars 2026